# 送電線用高速ディジタル電力線搬送による Zadoff-Chu 系列を用いた DPLL 方式の検討

佐々木 範雄\*, 花海 丞\* (通研電気工業),

鈴木 英祐\*\*(東北電力),安達 文幸\*\*\*(東北大学)

Study on DPLL Scheme Using Zadoff-Chu Sequence for High-speed Digital Power Line Carrier Systems.

Norio SASAKI, Tasuku HANAUMI (Tsuken Electric Industrial Co., Ltd)

Eisuke SUZUKI (Tohoku Electric Power Co., Inc), Fumiyuki Adachi (Tohoku University)

(Abstract) We have conducted a study of a high-speed digital power line carrier (DPLC) system adopting training-sequence inserted single-carrier (TS-SC) block transmission with minimum mean square error based frequency-domain equalization (MMSE-FDE). TS is inserted at both the beginning and tail of each block for channel estimation required for MMSE-FDE. The Zadoff-Chu sequence is used as TS. In the DPLC system, it is necessary to achieve accurate symbol timing recovery between transmitter and receiver and tracking to the sampling frequency offset (SFO) occurring between of the local crystal oscillator in the transmitter and receiver. In the presence of symbol timing error, the inter-symbol interference (ISI) occurs and the bit error rate (BER) deteriorates. In this paper, we propose a digital phase lock loop (DPLL) required for the DPLC system using TS-SC transmission. In our proposed DPLL, the cross-correlation for the reference TS with the transmitted TS is measured using 32-times oversampling. The time position which maximize the cross-correlation is determined as the symbol timing. This is repeated every time when the TS is received. Since the detected symbol timing changes in time in the presence of the SFO, the symbol timing is averaged using the first order infinite impulse response (IIR) filter. Simulation results confirmed that the timing error is within (+/-1/64 of symbol period) and that the of the required SNR for the bit error rate (BER=1×10<sup>-6</sup>) is less than 1 dB. Furthermore, it was also confirmed that the proposed DPLL has rapid timing recovery, e.g., timing error can be corrected within 400ms after a timing error of +1/32 symbol period is added. As a result, the proposed DPLL is applicable to practical high-speed digital power line carrier systems.

キーワード:電力線搬送,ディジタル伝送, Zadoff-Chu 系列, DPLL, 周波数領域等化 Keywords, Power line carrier, Digital transmission, Zadoff-Chu sequence, DPLL, Frequency domain equalization.

# 1. まえがき

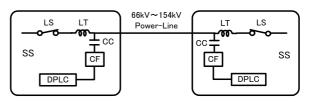

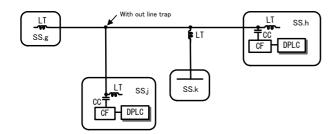

電気事業者において、発変電所間の高圧送電線(33kV~154kV)を伝送媒体とする電力線搬送方式は、伝送路の構成が困難な山間地域などルーラル系電気所へ容易に通信回線を展開させることが可能であり、災害時にも高い信頼度が確保される伝送方式である。この方式は、図 1 に示すように電気所 (SS) のラインスイッチ(LS)側へ高周波流入を阻止するライントラップ (LT)を送電線に直列に挿入し、送電線に高周波的に結合させるカップリングキャパシタ (CC)と、高周波のみを通過させるカップリングフィルタ (CF)とで送電線路に高周波回路を形成するもので、最大で約80kmにおよぶ伝送距離の実現が可能である。周波数帯域は100kHz~450kHz が電波法で割り当てられており、この帯域内に複数の通信チャネルが配置される。

電力線搬送方式においては、近年の電力保安通信網の IP 化への進展に伴い、アナログからディジタル化への移行が求められている。このため、筆者らはこれまで 50kHz 帯域幅を用いて伝送速度 192kbps を実現する 64QAM (Quadrature

Amplitude Modulation)シングルキャリア(SC: Single Carrer) ディジタル電力線搬送装置の開発を行なって来た $^{(1)\sim(4)}$ 。 さらに今後,電気事業者では電力システム全体の ICT 化を推進している。これに伴いディジタル電力線搬送装置には,帯域幅を 50kHz から 300kHz に広げ,192kbps よりもさらに高速な 1.1Mbps の伝送速度を実現する新たな高速ディジタル伝送方式の開究が求められている。

そこで筆者らは、長遅延で強い周波数選択性を有する送

LT: Line Trap CC: Coupling Capacitor CF: Coupling Filter LS: Line Switch DPLC: Digital Power Line Carrier SS: Sub Station

#### 図1 電力線搬送方式の伝送回路

Fig.1Transmission circuit of power line carrier system.

電線路で、高速ディジタル伝送を可能とする電力線搬送方式を実現するため、次世代移動通信の実現に向けて多くの研究が行われてきた SC ブロック伝送用周波数領域 MMSE等化 (MMSE-FDE: Minimum Mean Square Error Frequency Domain Equalization) (5)を適用することを検討している。また、MMSE-FDE に適用する伝送方式として時間領域で電力が一定となる Zadoff-Chu 系列(6)を既知トレーニング系列(TS: Training Sequence)としてデータブロックの先頭と後尾に挿入する TS-SC 方式(7)を採用することにしている。

SC 伝送では、帯域制限に用いる送受信フィルタにはイン パルス応答による符号間干渉 (ISI: Inter-Symbol Interference) を生じさせないルートナイキストフィルタの適用が必須と なるが, 送受信間でシンボルタイミングの同期を確立する 必要がある。また、シンボルタイミングを生成する局部水晶 発信器は送受信間でサンプリング周波数オフセット(SFO: Sampling Frequency Offset) (8)を持つため、タイミング位置が 時間とともに変動してゆくが、このタイミング位置のずれ の変化にも追従する必要がある。もし、シンボルタイミング にずれ(タイミングオフセット)が生じた場合は ISI が発生 し、ビット誤り率(BER: Bit Error Rate)特性が劣化する。この ため、送電線用高速ディジタル電力線方式の受信装置には 受信シンボル系列から送信シンボル系列のタイミング位置 を高精度に推定し、かつ SFO によるタイミング位置のずれ の時間変化にも追従できる DPLL(Digital Phase Lock Loop)の 導入が必要となる。

本論文では TS-SC 方式による送電線用高速ディジタル電力線搬送において、チャネル推定のための既知 TS と受信 TS との相互相関が最大となるタイミング位置から、送信シンボルタイミング位置を推定し、送受信間のタイミング同期を得る DPLL 方式を提案する。そしてタイミング推定特性、SFO への追従特性、および BER 特性を示す。

本論文の構成は以下のようになっている。第2章ではTS-SCブロック伝送について述べた後に、第3章では提案する相互相関測定を用いた DPLL 方式の原理について述べる。第4章では,送電線路のチャネルモデルの作成法で得られた複素インパルス応答を用い,相互相関測定による送信シンボルタイミングの推定と追従の特性,およびBER特性について計算機シミュレーションで評価し,提案方式の有用性を明らかにする。そして第5章でまとめる。

## 2. TS-SC ブロック伝送

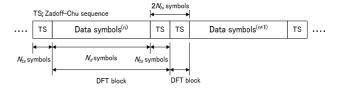

筆者らが検討をしている TS-SC 方式での送信ブロック系列は、Fig.2 に示す 1 ブロックに  $N_d$  個からなるデータシンボル系列の前後に  $N_{ts}$  個からなる既知系列 TS を付加した構成で、シンボル時間間隔  $t_p$  である。送信ブロック系列の、第 n 番目のデータシンボルブロックのベクトルを  $\mathbf{d}^{(n)}=[d^{(n)}(0),...,d^{(n)}(t),...,d^{(n)}(N_d-1)]^T$ で表す。ここで、T は転置操作を表す。また、送信ブロック系列で、データシンボルブロックの前後に付加される既知系列 TS のベクトルは  $\mathbf{u}=[u(0),...,u(t),...,u(N_{ts}-1)]^T$  で表し全てのブロックで共通の既知系列 TS になる。

図 2 TS-SC 伝送のブロック構成

Fig. 2 Block structure of TS-SC block transmission.

既知系列 TS には Zadoff-Chu 系列<sup>(13)</sup>を適用するので、シンボル長が  $N_{ts}$ で t 番目  $(t=0\sim N_{ts}-1)$  の要素 u(t)は次式で定義される<sup>(6)</sup>。

$$u(t) = \begin{cases} \exp\left(-j\frac{\pi mt^2}{N_{ts}}\right), N_{ts} \in \text{ even number} \\ \exp\left(-j\frac{\pi mt(t+1)}{N_{ts}}\right), N_{ts} \in \text{ odd number} \end{cases}$$

(1)

ここで,m は  $N_{ts}$  と互いに素な  $N_{ts}$  より小さい正の整数である。第 n 番目の送信ブロック  $\mathbf{s}^{(n)} = [s^{(n)}(0),...,s^{(n)}(N_{ts}-1),...,s^{(n)}(2N_{ts}+N_{d}-1)]^{T}$  は次式で表される。

$$\mathbf{s}^{(n)} = \begin{bmatrix} \mathbf{u} \\ \mathbf{d}^{(n)} \\ \mathbf{u} \end{bmatrix}$$

(2)

このように、TS を送信ブロックの前後に挿入して伝送するのがTS-SC 伝送である。本提案のDPLL 方式では(2)式に示す d<sup>(n)</sup>の先頭に挿入された u となるTS を用いた相互相関測定から送信シンボルタイミングの位置推定と追従を行う。

次いで、送電線路はシンボル時間間隔  $t_p$  の L 個の離散パスからなる伝送路であると仮定する。この時、第n 番目のブロックにおけるチャネルインパルス応答  $h^{(n)}(\tau)$  は次式のように表せる。

$$h^{(n)}(\tau) = \sum_{l=0}^{L-1} h_l^{(n)} \delta(\tau - \tau_l)$$

(3)

ここで、 $h_l^{(n)}$ および $\tau_l$ はそれぞれ第 l パス番目の複素パス利得および遅延時間であり、 $E[\sum_{l=0}^{L-1} \left| h_l^{(n)} \right|^2]$ =1(0dB)である。ここで、E[.]は期待値を求める操作を表す。なお、送電線路のチャネル特性は参考文献(2)で述べているように、伝達関数の時変動はなく、ほぼ一定に保たれていることから、隣接ブロック間で送電線路の伝達関数の時変動はないものと仮定する。なお、相互相関測定として用いるブロック先頭の TSシンボル長は $N_{ts}$ =L であるため、n 番目ブロックのインパルス応答  $\mathbf{h}_{rs}^{(n)}$ は、(3)式の複素パス利得 $h_l^{(n)}$ (l=0~L-1)を用いると次式に示す  $N_{ts}$ × $N_{ts}$  の巡回行列で与えられる。

$$\mathbf{h}_{TS}^{(n)} = \begin{bmatrix} h_0^{(n)} & h_{L-1}^{(n)} & \cdots & h_1^{(n)} \\ h_1^{(n)} & h_0^{(n)} & \cdots & h_2^{(n)} \\ \vdots & \vdots & \ddots & \vdots \\ h_{L-1}^{(n)} & h_{L-2}^{(n)} & \cdots & h_0^{(n)} \end{bmatrix}$$

(4)

図 4 相互相関器のブロック構成 Fig. 4 Block structure of cross correlator.

図 5 補正値生成部でのタイミング波形

Fig. 5 Timing waveforms at compensation value generator.

## 相互相関測定による DPLL 方式の原理

本章では相互相関測定による DPLL 方式の原理と動作に ついて概要を述べる。

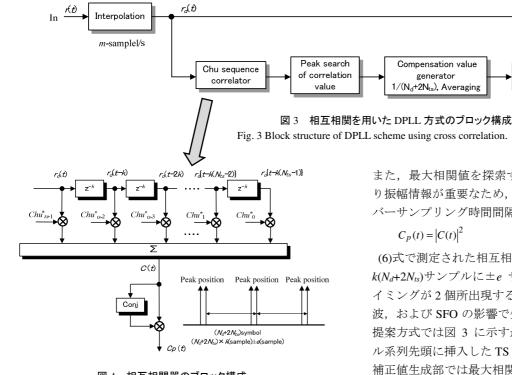

提案方式では、TS-SC 方式で用いる TS と、受信シンボル 系列との相互相関測定を行うため、図3に示すよう受信シ ンボル系列 r(t)を整数となる k 倍オーバーサンプリングのイ ンターポレーションにより  $r_a(t)$ の信号を得る。k倍オーバー サンプリングされた受信シンボル系列 ra(t)は図 4 に示すよ う  $z^{-k}$  サンプリング遅延する遅延器を  $N_{ts}$ -1 個配置した相関 器へ入力する。相関器では予め用意された参照信号となる Zadoff-Chu 系列 *chu*\*(*i*)との相関和 *C*(*t*)を次式により得る。

$$C(t) = \sum_{i=0}^{N_{ts}-1} r_d(t-ik) \cdot Chu^*(N_{ts}-1-i)$$

(5)

また、最大相関値を探索するためには位相情報は不要であ り振幅情報が重要なため、次式による相互相関  $C_p(t)$ をオー バーサンプリング時間間隔 tk で逐次取得する。

Compensation value

generator

1/(N<sub>d</sub>+2N<sub>ts</sub>), Averaging

$$C_p(t) = \left| C(t) \right|^2 \tag{6}$$

Symbol timing

generator

Data

Symbol

timing data

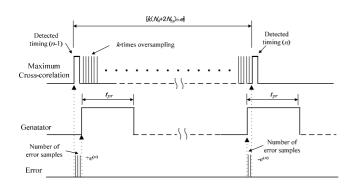

(6)式で測定された相互相関の最大値は、図4に示すように  $k(N_d+2N_t)$ サンプルに $\pm e$  サンプルの誤差を有した周期のタ イミングが2個所出現する。なお, e は伝送路の雑音や遅延 波、および SFO の影響で生じる誤差量で整数値となる。本 提案方式では図 3 に示す最大相関値探索部でデータシンボ ル系列先頭に挿入した TS の最大相関値  $C_{pmax}(t)$ を探索する。 補正値生成部では最大相関値が探索された第 n 番目ブロッ クにおける最大相関値  $C_{max}$  (n)のタイミングと、第 n 番目の 一つ前のブロックで探索された最大相関値 C pmax (n-1)のタイ ミング間の時間間隔を k 倍オーバーサンプリングで計測す る。そして、計測されたサンプリング数 $\{k(N_d+2N_{ts})\pm e\}$ から  $\pm e$  のみを  $N_d+2N_t$  で除算し、その値で図 5 に示すサンプリ ング時間幅 tprの1シンボル時間幅を補正する。また、図5 に示すように最大相関値のタイミング位置と, 受信装置の シンボルタイミング位置は、前述したように誤差量±e<sup>(n)</sup>が 生じる。そこで、図5に示すようにk倍サンプリングとなる 補正量  $c_r^{(n)}$ = $\pm e^{(n)}$ ×-1 を取得し、受信装置で生成しているシ ンボルタイミング tprのタイミング位置を補正する。以降は 1ブロック周期で生成される相互相関の最大値 Cmmax(n) のタ イミング位置と $t_{pr}$ のタイミング位置との誤差量 $\pm e^{(n)}$ が取得 される。そして、誤差量から取得された補正量 $c_r^{(n)}$ を次式に 示す忘却係数  $\alpha$  (0< $\alpha$ <1) を有する 1 次 IIR(Infiniti Impulse Response)フィルタを用いて平均化した補正量 $\overline{c}_r^{(n)}(t)$ をブロ ック単位で導出し、tpr のタイミング位置と時間間隔を逐次 補正する。

$$\overline{c}_r^{(n)}(t) = \alpha \overline{c}_r^{(n-1)}(t) + (1 - \alpha)c_r^{(n)}(t) \tag{7}$$

このように提案方式では, ブロック単位で送受信のシン ボルタイミングの誤差を逐次導出し, 平均化された補正量 によって送信シンボルタイミングとの同期が確立して行く。 従って、SFO に起因したシンボルタイミング位置が変動し ても誤差量を逐次推定・補正されるので,変動量に対し追従 することが可能となっている。

さらにシンボルタイミング生成部では, 平均化した補正 量 $\bar{c}_{r}^{(n)}(t)$ をルートナイキストフィルタなどで必要とするオ ーバーサンプリング値へと変換し,送信シンボルタイミン グと同期された受信シンボル信号が生成される。

図6 チャネルモデルに用いた送電系統

Fig.6 Power line System of used channel model.

## 4. 計算機シミュレーション解析結果

計算機シミュレーションに用いる送電線路のモデルには図 6 に示すよう、送電線分岐個所にラインとラップが設置されていないことで、パス電力量が大きくなるモデル(1)を用いた。この場合、遅延波が 300 $\mu$ s 程度まで存在する伝送路(1)となるので、送電線用高速ディジタル搬送方式で用いるシンボルレートを 210 $\mu$ symbol/s ( $\mu$ ) に規定した場合、パス数 $\mu$  に移名した。そして、文献 2 に示す手順で 64 個のパスにランダムな位相を与えて生成した 100 組の複素インパルス応答を作成した。次いで、100 組の複素インパルス応答を作成した。次いで、100 組の複素インパルス応答を作成した。次いで、100 組の複素インパルス応答を抽出し、計算機シミュレーションに採用した。計算機シミュレーションの諸元を表 1 に示す。

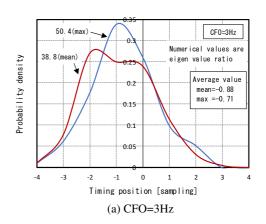

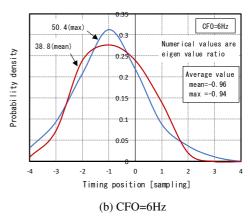

〈4・1〉Zadoff-Chu 系列の相互相関特性 長遅延で強い周波数選択性を示す送電線路モデルにおいて、SFO が存在しない時に、伝送された Zadoff-Chu 系列と受信側で予め用意した Zadoff-Chu 系列とが最大相関となるタイミング位置の確率密度関数を示し、真の送信シンボルタイミング位置との誤差特性を計算機シミュレーションで明らかにする。この時、(5)式に示すオーバーサンプリング値 k は実用的な相関器の規模を想定し32 倍とした。また、搬送周波数の周波数オフセット(CFO: Carrier Frequency Offset)量は、送受信間で+3Hz,+6Hzの2つの CFO を用いた。そして、SNR(Signal Noise Ratio)は30dBとした。

図 7 に、(6)式により各ブロックで得られた最大相関値  $C_{pmax}$  (n)のタイミング位置について、測定した全サンプル数 (1s÷0.0052s/block=193 個) で正規化した確率密度関数を示す。そして、真の送信シンボルタイミング位置(横軸の同期ポジションがゼロの位置)との比較をする。図 7 に示す Zadoff-Chu 系列の最大相関値の平均は、CFO および、チャネルの固有値比に係わらず真の送信シンボルタイミング位置より 32 倍オーバーサンプリングで約-1 サンプリング(シンボル間隔の-1/32)の位置に分布しており、それぞれの平均値は、およそ-1~-0.5 サインプリングの範囲内に分布している。これは、Zadoff-Chu 系列の複素包絡線が遅延波による影響を受けたことで、最大相関値が約-1 サンプリングほど誤差を示す特性になったものと考える。このことから、SFO が存在しない場合において、32 倍オーバーサンプリング時に

表1 計算機シミュレーションの諸言

Table 1 Computer simulation condition.

|             | Data modulation             | 64QAM                               |

|-------------|-----------------------------|-------------------------------------|

| Transmitter | Data symbol<br>Block length | N <sub>d</sub> =960                 |

|             | TS length                   | $N_{ts} = 64$                       |

|             | TS type                     | Zadoff-Chu sequence ( <i>m</i> =61) |

|             | Symbol Rate                 | 210ksymbol/s                        |

| Channel     | <i>L</i> =64-path           | symbol-space 4.76μs                 |

| Receiver    | Signal detection            | MMSE-FDE                            |

|             | Channel estimation          | Frequency-domain channel estimation |

| Filter      | Root Nyquist filter         | Roll-off factor $\beta$ =0.4        |

図 7 最大相互相関値の確率密度

Fig.7 Probability density of maximum cross-correlation value.

最大相関値の平均から+1 サンプリング程度の補正値を予め 設けることで本提案方式は真の送信シンボルタイミング位 置から±0.5 サンプリング(シンボル間隔の±1/64)程度の誤差 で受信シンルタイミングを生成できるものと考える。さら に本提案方式は CFO の線形位相回転量による相互相関特性 には大きなばらつきはないことから、 CFO の大きさによる 相互相関測定への影響は与えないものと考える

#### 〈4·2〉シンボルタイミングの誤差特性

本節では、本提案方式による送信シンボルタイミングの 誤差特性を明らかにするため、(7)式に示す平均補正量  $\overline{c}_r^{(n)}(t)$ から得られた受信シンボルタイミング位置と、新の 送信シンボルタイミング位置との差を誤差特性として導出 した。なお、受信シンボルタイミングの補正量に用いる(7)式 の1次IIRフィルタの忘却係数 $\alpha$ は、収束速度と収束時の推定 精度を加味し、0.98を適用し、SFOの最大は実現性のある局 部水晶発信器を実装するものと仮定し+100Hzとした。

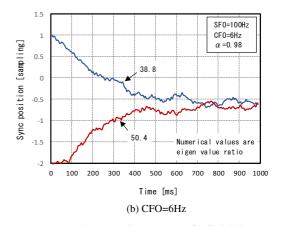

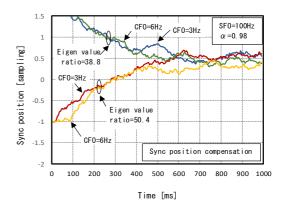

図8にチャネルの固有値比が最大(50.4)と平均(38.8)におけ る送信シンボルタイミングの推定誤差特性を示す。(a)が CFO=3Hz, (b)がCFO=6Hzを用いた時,推定を開始した時刻 から1s経過後までに亘る誤差特性である。CFO=3Hzにおい て,2組の固有値比のチャネルとも,600ms程度で推定が収束 している。また、収束時における真の送信シンボルタイミン グとの平均誤差量は、-0.5サンプリング(シンボル間隔の-1/64)程度の誤差量になることが分かる。次にCFO=6Hzにお いては、2組の固有値比のチャネルとも、500ms程度で推定が 収束している。また、収束時における真の送信シンボルタイ ミングとの平均誤差量は、CFO=3Hz 時と同様に-0.5サンプ リング程度の誤差量になることが分かる。つまり, 本提案の Zadoff-Chu系列を用いたDPLL方式は、送電線路におけるチ ャネルの固有値比の大きさとCFOの大きさに関わらず、32倍 オーバーサンプリングにおいてSFOが+100Hz存在する場 合,-0.5サンプリング程度のオフセットが生じる推定誤差特 性になることが明らかになった。

従って、平均補正量 $\overline{c}_r^{(n)}(t)$ に予め+1 サンプリングの補正 値を与えておけば、推定誤差量は+0.5 サンプリング, つまり シンボル間隔の+1/64 程度の誤差量に抑えることが出来る と考える。そこで32倍オーバーサンプリングにおいて、+1 サンプリングの補正値を与えた場合の送信シンボルタイミ ング推定特性を図9に示す。+1 サンプリングの補正値を与 えたことで, それぞれの要素における収束時の推定誤差量 は、+0.5 サンプリング近傍に分布されていることが分かる。 このことから、<4.1>節の結果と併せて推測すると±100Hz 間の SFO が存在する場合, およそ±0.5 サンプリングの誤差 範囲で推定可能と考える。ところで, サンプリング数は整数 値となるため、±0.5 サンプリングの値は補正できない。そ こで,送電線用高速ディジタル電力線搬送方式では,平均補 正量 $\bar{c}_r^{(n)}(t)$ (実数値)を 128 倍オーバーサンプリングとなる 7bit(2<sup>7</sup>=128)で表現し32倍オーバーサンプリングに対して± 0.25 サンプリング(シンボル間隔の±1/128)の補正スケーリ ングとなる方式を適用する。そして、128倍オーバーサンプ リングで補正した受信シンボルタイミングによって 128 倍 オーバーサンプリングで動作するルートナイキストフィル タでシンボルタイミング位置を調整する方式を適用する。

以上のことから送電線路において、本提案のZadoff-Chu 系列を用いたDPLL方式は、平均補正量 $\overline{c_r}^{(n)}(t)$ に予め+1~+0.5 サンプリングの補正値を与える手法は送信シンボルタイミング位置の推定精度向上には有用な方式であると考える。

図 8 送信シンボルタイミングの推定特性 Fig.8 Estimation performances of transmitted symbol timing.

図 9 補正後の送信シンボルタイミングの推定特性 Fig.9 Estimation performances of corrected transmitted symbol timing.

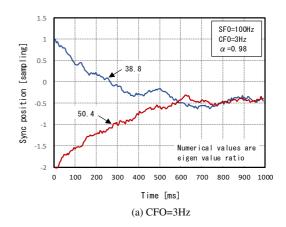

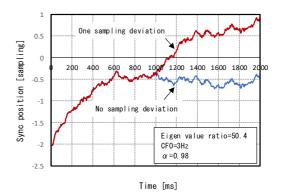

## 〈4·3〉シンボルタイミング推定の追従特性

本節では局部水晶発信器の周囲の温度変化などで周波数が偏移し、シンボルタイミング位置が急激に変化した場合の提案方式によるタイミング位置の追従特性を明らかにする。図 10 に、チャネルの固有値比が最大(50.4)で、SFO が100Hz、CFO が 3Hz 生じている送受信システムにおいて送信のシンボルタイミングが、測定開始から 1s 後にシンボルタイミング位置が+1 サンプリング(シンボル間隔の+1/32)の誤差が生じた場合の追従特性を示している。1s の時刻に送信シンボルタイミング位置を+1 サンプリング変化させた場

合のシンボルタイミング位置の推定は変化に追従をしており、約 400ms 経過後に、真の送信シンボルタイミング位置 (同期位置が+1 サンプリング)から-0.5 サンプリング程度の 誤差で推定がなされている。なお、参考として送信シンボルタイミング位置の変化が生じない場合の推定特性も併せて示している。

以上のことから,本提案方式は急激なタイミング位置変化に対してもシンボルタイミング位置を追従し推定することが可能であり,有用であると考える。

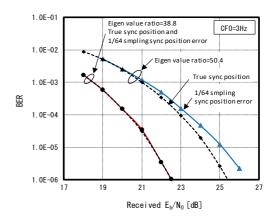

### 〈4·4〉送信シンボルタイミング推定誤差による BER 特性

提案の DPLL 方式が 32 倍オーバーサンプリングによる相互相関測定において、図 9 に示すよう、真の送信シンボルタイミング位置から+0.5 サンプリング(シンボル間隔の+1/64)の誤差で推定された場合と、推定誤差が生じていない場合に、64QAM を用いた MMSE-FDE の BER 特性を示す。この時のチャネルは固有値比が最大 (50.4)と平均(38.8)の 2 組を用い、表 1 に示す諸元とした場合のそれぞれの特性を明らかにする。なお、CFO は 3Hz とした。

図 11 に 2 組の固有値比による推定誤差が有無の場合での BER 特性を示す。最大固有値比での BER 特性は伝送路の振幅歪が大きいため, MMSE-FDE でのチャネル推定誤差と等化器出力の MSE が大きくなり,所要の BER( $1 \times 10^6$ )を得るに高い  $E_b I N_0$  を必要とすること分かる。また,推定誤差が+0.5 サンプリング生じている BER 特性は  $1 \times 10^6$  で約  $1 \, \mathrm{dB}$  の劣化が示されている。次いで,平均固有値比の伝送路の振幅歪は最大固有値比と比較し小さくなるので, チャネル推定誤差と等化器出力の MSE は小さくなることから,BER 特性は少ない  $E_b I N_0$  で所要の BER が確保できることが分かる。+0.5 サンプリングの推定誤差が生じている場合でも BER 特性に劣化は生じないことが示されている。

以上のことから本提案の DPLL 方式は、およそ±0.5 サンプリング(シンボル間隔の±1/64)の誤差範囲に抑えられることで、最大固有値比のチャネルにおける所要の BER は 1dB 程度の劣化に抑えることが可能で、平均固有値比のチャネルでは BER 特性に劣化が生じないことが明らかになった。よって、提案 DPLL 方式は MMSE-FDE を用いる送電線用高速ディジタル電力線方式には有用であると考える。

#### 5. まとめ

本論文では、SC 伝送の MMSE-FDE を用いる送電線用高速ディジタル電力線方式に適応する DPLL 方式を提案した。提案 DPLL 方式では、TS として用いた Zadoff-Chu 系列の相互相関を 32 倍オーバーサンプリングで測定し、検出された最大相関値のサンプリング位置に予め+1 サンプリングの補正値を与えれば、SFO が±100Hz 間で生じている場合、送受信間のサンプリング位置の誤差は、およそ±0.5 サンプリング(シンボル間隔の±1/64)の誤差範囲で推定可能なことを示した。また、サンプリング誤差が+0.5 の場合、所要の BER特性は最大固有値比で約 1dB の特性劣化に抑えられ、平均固有値比では特性に劣化が生じないことを明らかにした。

図10 送信シンボルタイミング推定の追従特性

$Fig.\ 10\ Tracking\ performance\ of\ transmitted\ symbol\ timing\ estimation.$

図11 送信シンボルタイミング推定誤差によるBER特性 Fig. 11 BER performance with transmitted symbol timing estimation error.

以上のことから本提案方式は、送電線用高速ディジタル 電力線搬送方式を実現する有用なDPLL方式と考える。

#### か 献

- (1) 佐々木範雄,清野賢一,花海丞,織田健志,安達文幸:「送電線路を用いるディジタル伝送のチャネルモデル化」,電学論(C), Vol.132, No.8, pp.1317-1327(2012)

- (2) 佐々木範雄, 花海丞, 織田健志, 安達文幸:「送電線用ディジタル電力線搬送における適応等化器」,電学論(C), Vol.134,No.2,pp.258-266(2014)

- (3) 佐々木範雄, 花海丞, 織田健志, 安達文幸: 「送電線用ディジタル電力線 搬送における周波数オフセット補償方式」,電学論(C), Vol.135,No.11,pp.1351-1360(2015)

- (4) 佐々木範雄,花海丞、織田健志、安達文幸:「送電線ディジタル電力 線搬送に用いる適応等化器のトレーニング符号」,電学通信研資、 CMN-14-062,pp21-25(2014)

- (5) 山本 哲矢, 安達 文幸:「既知系列を利用したシングルキャリア伝送 における周波数領域繰り返しチャンネル推定に関する検討」,信学技 報, RCS2011·369, pp317·322(2012)

- (6) 伊藤理人,八巻俊輔,阿部正英,川又政征:「2次位相スペクトルの 差を持つ信号間の位相限定相関関数」,情報処理学会75回全国大会, 2-551 (2013)

- (7) 藤村 勇樹, 梅原 大祐, 田野 哲: 「周波数領域等化におけるフェージングひずみ補償法」, 信学論, Vol.J91-B, No.3, pp250-259(2008)

- (8) 杉本大樹, 佐藤拓郎, 富永英義:「OFDM システムにおけるパイロット信号を用いたサンプリング周波数オフセット及び残留周波数オフセット補償方式」、信学論、Vol.J92-B,No.9,pp1513-1523 (2009)